## **GS6081**

#### **Gennum Products**

#### **Features**

- Supports data rates from 270Mb/s to 5.94Gb/s

- SMPTE ST 424, SMPTE ST 292 and SMPTE ST 259 compliant

- Supports DVB-ASI at 270Mb/s

- Wide common-mode range input buffer

- 100mV sensitivity

- supports DC-coupling to industry-standard differential logic

- on-chip  $100\Omega$  differential data input termination

- Input signal trace equalization

- Dual differential coaxial-cable-driving outputs

- selectable slew rates

- adjustable output swing from 500mV<sub>pp</sub> to 1040mV<sub>pp</sub>

- independent disable controls for each output

- Robust signal presence function

- Excellent output eye quality

- Power supply operation at +3.3V or +2.5V

- 135mW power consumption (+2.5V supply)

- Operating temperature range: -40°C to +85°C

- Small footprint QFN package (4mm x 4mm)

- new dual-output pin out

- use the GS6080 for a single-output variant that is drop-in compatible to the GS2988

- Pb-free and RoHS compliant

#### **Applications**

6G UHD-SDI, SMPTE ST 424, SMPTE ST 292 and SMPTE ST 259 coaxial cable serial digital interfaces

#### **Description**

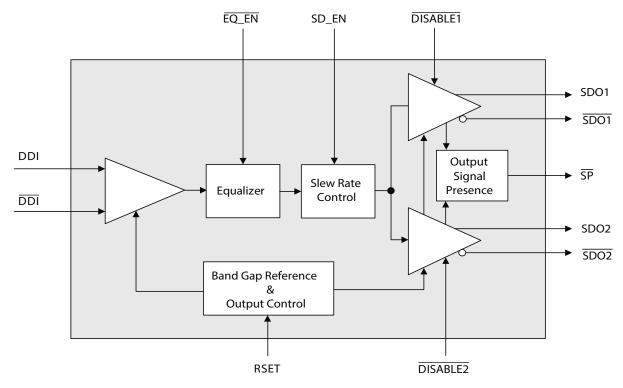

The GS6081 is a high-speed BiCMOS integrated circuit designed to drive one to four  $75\Omega$  coaxial cables.

The GS6081 may drive data rates up to 5.94Gb/s and provides two selectable slew rates in order to achieve compliance to SMPTE ST 424, SMPTE ST 292 and SMPTE ST 259.

The GS6081 accepts industry-standard differential input levels including LVPECL and CML.

Input trace equalization compensates for up to 10 inches of FR4 trace loss while in HD, 3G and UHD modes. This feature is enabled and disabled using the EQ\_EN pin.

The DISABLET and DISABLE2 pins power-down the first and second output drivers respectively, leaving the serial data outputs in a high-impedance state. When applied simultaneously, the entire device is powered-down.

The GS6081 features adjustable output swing using an external bias resistor. The single-ended output swing is adjustable from  $500 \text{mV}_{DD}$  to  $1040 \text{mV}_{DD}$ .

An output signal presence function, the  $\overline{SP}$  pin, indicates whether an active signal is present at the output of the GS6081.

The GS6081 can be powered from either a +3.3V or a +2.5V supply. Power consumption is typically 135mW using a +2.5V power supply with one output enabled.

The GS6081 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant.

This component and all homogeneous subcomponents are RoHS compliant.

**GS6081 Functional Block Diagram**

### **Revision History**

| Version | ECO    | PCN | Date          | Changes and/or Modifications                                                                                                                                              |

|---------|--------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | 020838 | _   | July 2014     | Updated max power and current values in Table 2-2.                                                                                                                        |

| 3       | 016276 | _   | November 2013 | Corrected pin order in Table 1-1 to match proper pin numbering arrangement                                                                                                |

| 2       | 013845 | _   | July 2013     | Updated from Draft Data Sheet to Final Data Sheet.                                                                                                                        |

| 1       | 012266 | _   | June 2013     | Updated Table 2-3: AC Electrical Characteristics. Changed the product name to GS6081 (and the DOC ID to PDS-060046) to reflect the production-ready status of the device. |

| 0       | 010383 | _   | December 2012 | New document.                                                                                                                                                             |

### **Contents**

| Features                                               | 1  |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Description                                            | 1  |

| Revision History                                       | 2  |

| 1. Pin Out                                             | 4  |

| 1.1 Pin Assignment                                     | 4  |

| 1.2 Pin Descriptions                                   | 4  |

| 2. Electrical Characteristics                          | 6  |

| 2.1 Absolute Maximum Ratings                           | 6  |

| 2.2 DC Electrical Characteristics                      | 6  |

| 2.3 AC Electrical Characteristics                      | 7  |

| 3. Input/Output Circuits                               | 9  |

| 4. Detailed Description                                | 10 |

| 4.1 Serial Data Input                                  | 10 |

| 4.2 Input Trace-equalization                           | 10 |

| 4.3 Serial Data Output                                 | 10 |

| 4.3.1 Slew Rate Selection (Rise/Fall Time Requirement) | 11 |

| 4.4 Output Disable                                     | 11 |

| 4.5 Signal Presence Indicator (SP)                     | 11 |

| 4.6 Output Amplitude (RSET)                            |    |

| 4.7 Output Return Loss Measurement                     | 13 |

| 5. Application Information                             | 14 |

| 5.1 PCB Layout                                         | 14 |

| 5.2 Typical Application Circuit                        |    |

| 6. Package & Ordering Information                      | 15 |

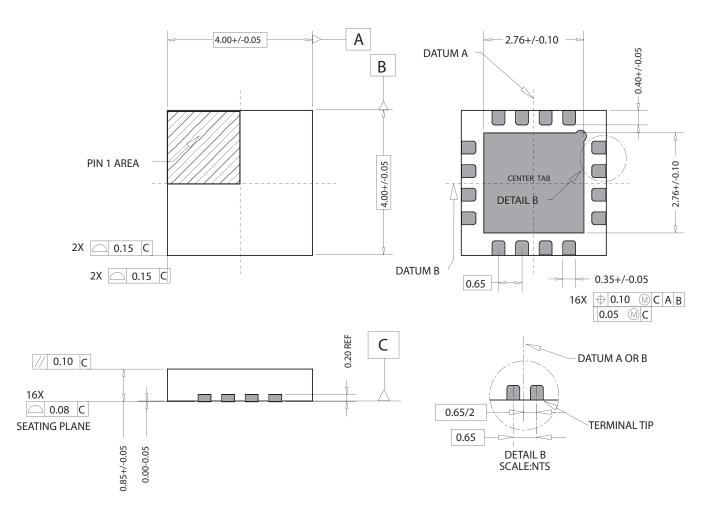

| 6.1 Package Dimensions                                 | 15 |

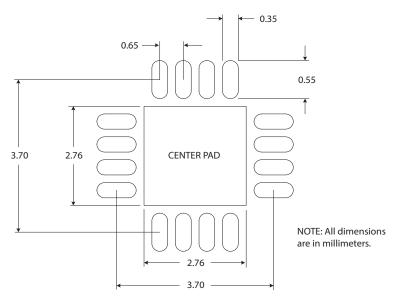

| 6.2 Recommended PCB Footprint                          | 16 |

| 6.3 Packaging Data                                     | 16 |

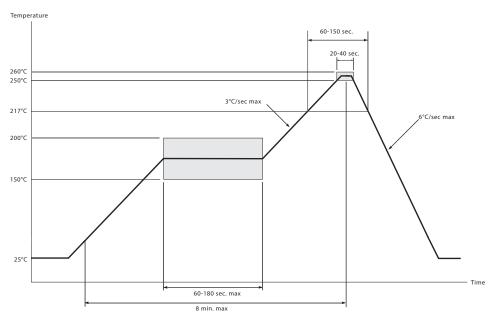

| 6.4 Solder Reflow Profiles                             | 17 |

| 6.5 Marking Diagram                                    | 17 |

| 6.6 Ordering Information                               | 18 |

# 1. Pin Out

# 1.1 Pin Assignment

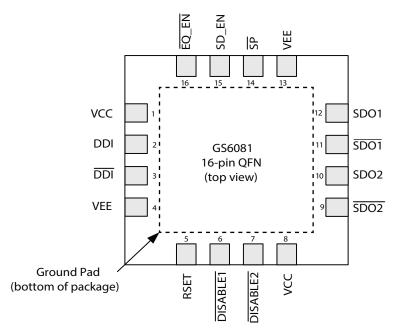

Figure 1-1: 16-Pin QFN

## 1.2 Pin Descriptions

**Table 1-1: Pin Descriptions**

| Pin Number | Name     | Туре  | Description                                                                                          |

|------------|----------|-------|------------------------------------------------------------------------------------------------------|

| 1,8        | VCC      | Power | Most positive power supply connection for the input buffer and core. Connect to $+3.3V$ or $+2.5V$ . |

| 2, 3       | DDI, DDI | Input | Serial data differential input. See Section 4.1 for details.                                         |

| 4, 13      | VEE      | Power | Most negative power supply connection for the input buffer and core.  Connect to ground.             |

| 5          | RSET     | Input | External output amplitude control resistor connection. See Section 4.6 for details.                  |

**Table 1-1: Pin Descriptions (Continued)**

| Pin Number | Name       | Туре   | Description                                                                                                                                                                                                                                                                                                |

|------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6*         | DISABLE1   | Input  | Output Disable 1 (control signal input).  When set LOW, the first serial data output is disabled (powered-down) and the SDO1/SDO1 pins are set to high-impedance. When set HIGH, the SDO1/SDO1 pins will output a serial data signal.  See Section 4.4 for details.                                        |

| -          |            |        | This pin has an internal pull-up.                                                                                                                                                                                                                                                                          |

| 7*         | DISABLE2   | Input  | Output Disable 2 (control signal input).  When set LOW, the second serial data output is disabled (powered-down) and the SDO2/SDO2 pins are set to high-impedance.  When set HIGH, the SDO2/SDO2 pins will output a serial data signal.  See Section 4.4 for details.  This pin has an internal pull-down. |

| 9,10       | SDO2, SDO2 | Output | Serial data differential output of second output buffer.                                                                                                                                                                                                                                                   |

| 11,12      | SDO1, SDO1 | Output | Serial data differential output of first output buffer.                                                                                                                                                                                                                                                    |

| 14         | SP         | Output | Signal Presence (status signal output).  Indicates presence of a signal at the pre-driver to the device's output stage.  See Section 4.5 for details.                                                                                                                                                      |

| 15         | SD_EN      | Input  | SD Slew Rate Enable (control signal input). Sets the slew rate for SDO/SDO. See Section 4.3.1 for details. This pin has an internal pull-up.                                                                                                                                                               |

| 16         | EQ_EN      | Input  | Equalizer Enable (control signal input).  See Section 4.2 for details.  This pin has an internal pull-up.  Note: this pin must be pulled HIGH or left floating for operation in SD mode.                                                                                                                   |

| _          | Center Pad | Power  | Connect to most negative power supply plane following the recommendations in Recommended PCB Footprint on page 16.                                                                                                                                                                                         |

<sup>\*</sup>Note: When pins 6 and 7 are driven LOW together (or similarly when pin 6 is driven LOW while pin 7 is left floating), the entire device is powered-down. In this state, minimum power consumption occurs.

## 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                   | Value                           |

|---------------------------------------------|---------------------------------|

| Supply Voltage                              | -0.5V to +3.6 V <sub>DC</sub>   |

| Input ESD Voltage                           | 2.5kV                           |

| Storage Temperature Range (T <sub>s</sub> ) | -50°C to +125°C                 |

| Input Voltage Range (any input)             | -0.3 to (V <sub>CC</sub> +0.3)V |

| Operating Temperature Range                 | -40°C to +85°C                  |

| Solder Reflow Temperature                   | 260°C                           |

**Note:** Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation outside of the ranges shown in Table 2-1 is not implied.

#### 2.2 DC Electrical Characteristics

**Table 2-2: DC Electrical Characteristics**

$V_{CC}$  = +3.3V ±5% or +2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                    | Symbol          | Conditions                                               | Min   | Тур | Max   | Units | Notes |

|------------------------------|-----------------|----------------------------------------------------------|-------|-----|-------|-------|-------|

| Supply Voltage               | V <sub>CC</sub> | 3.3V Typical                                             | 3.135 | 3.3 | 3.465 | V     | _     |

| Supply voltage               | <b>v</b> cc     | 2.5V Typical                                             | 2.375 | 2.5 | 2.625 | V     | _     |

|                              |                 | SDO1/SDO1 or<br>SDO2/SDO2 enabled                        | _     | 135 | 160   | mW    | 1     |

| Power Consumption (+2.5V)    | $P_{D}$         | SDO1/SDO1 and<br>SDO2/SDO2 enabled                       | _     | 205 | 242   | mW    | 1     |

| (,                           |                 | SDO1/SDO1 and<br>SDO2/SDO2 disabled<br>(Power-Down Mode) | _     | 3   | 5     | mW    | 1     |

|                              | P <sub>D</sub>  | SDO1/SDO1 enabled,<br>SDO2/SDO2 disabled                 | _     | 185 | 222   | mW    | 1     |

| Power Consumption<br>(+3.3V) |                 | SDO1/SDO1 and<br>SDO2/SDO2 enabled                       | _     | 284 | 340   | mW    | 1     |

|                              |                 | SDO1/SDO1 and<br>SDO2/SDO2 disabled<br>(Power-Down Mode) | _     | 4   | 6     | mW    | 1     |

#### **Table 2-2: DC Electrical Characteristics (Continued)**

$V_{CC}$  = +3.3V ±5% or +2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                   | Symbol             | Conditions                                               | Min                      | Тур                                | Max                           | Units | Notes |

|-----------------------------|--------------------|----------------------------------------------------------|--------------------------|------------------------------------|-------------------------------|-------|-------|

|                             |                    | SDO1/SDO1 or<br>SDO2/SDO2 enabled                        | _                        | 54                                 | 61                            | mA    | 1     |

| Supply Current<br>(+2.5V)   | I <sub>S</sub>     | SDO1/SDO1 and<br>SDO2/SDO2 enabled                       | _                        | 82                                 | 92                            | mA    | 1     |

| (12.34)                     |                    | SDO1/SDO1 and<br>SDO2/SDO2 disabled<br>(Power-Down Mode) | _                        | 1                                  | 1.8                           | mA    | 1     |

|                             |                    | SDO1/SDO1 or<br>SDO2/SDO2 enabled                        | _                        | 56                                 | 64                            | mA    | 1     |

| Supply Current<br>(+3.3V)   | I <sub>S</sub>     | SDO1/SDO1 and<br>SDO2/SDO2 enabled                       | _                        | 86                                 | 98                            | mA    | 1     |

| (1301)                      |                    | SDO1/SDO1 and<br>SDO2/SDO2 disabled<br>(Power-Down Mode) | _                        | 1                                  | 1.8                           | mA    | 1     |

| Output Voltage              | V <sub>CMOUT</sub> | Common mode                                              | _                        | V <sub>CC</sub> - V <sub>OUT</sub> | _                             | V     | _     |

| Input Voltage               | V <sub>CMIN</sub>  | Common mode                                              | $1.4 + \Delta V_{DDI}/2$ | _                                  | $V_{CC}$ - $\Delta V_{DDI}/2$ | V     | _     |

| SD_EN, <del>DISABLE</del> , | V <sub>IH</sub>    | I <sub>IH</sub> <= 150μA                                 | 1.7                      | _                                  | _                             | V     | _     |

| EQ_EN Input                 | V <sub>IL</sub>    | I <sub>IL</sub> <= 150μΑ                                 | _                        | _                                  | 0.4                           | V     | _     |

| SP Drive Strength           | _                  | _                                                        | 2                        | _                                  | _                             | mA    | _     |

#### **Notes:**

## 2.3 AC Electrical Characteristics

**Table 2-3: AC Electrical Characteristics**

$V_{CC}$  = +3.3V ±5% or +2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter              | Symbol            | Conditions | Min | Тур | Max  | Units            | Notes |

|------------------------|-------------------|------------|-----|-----|------|------------------|-------|

| Serial input data rate | DR <sub>SDO</sub> | _          | 270 | _   | 5940 | Mb/s             | 1     |

| Additive jitter        | _                 | 5.94Gb/s   | _   | 15  | _    | ps <sub>pp</sub> | 2, 8  |

|                        | _                 | 2.97Gb/s   | _   | 10  | _    | ps <sub>pp</sub> | 2     |

|                        |                   | 1.485Gb/s  | _   | 10  | _    | ps <sub>pp</sub> | 2     |

|                        |                   | 270Mb/s    | _   | 30  | _    | ps <sub>pp</sub> | 2     |

<sup>1.</sup> Power consumed in GS6081 only. Termination resistors draw extra current.

#### **Table 2-3: AC Electrical Characteristics (Continued)**

$V_{CC}$  = +3.3V ±5% or +2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                  | Symbol                             | Conditions                                       | Min | Тур | Max  | Units                | Notes   |

|----------------------------|------------------------------------|--------------------------------------------------|-----|-----|------|----------------------|---------|

|                            | t <sub>r</sub> , t <sub>f</sub>    | 5.94Gb/s                                         | _   | 66  | _    | ps                   | 3, 8    |

| Rise/Fall time             | t <sub>r</sub> , t <sub>f</sub>    | SD_EN=0                                          | _   | _   | 135  | ps                   | 3       |

|                            | t <sub>r</sub> , t <sub>f</sub>    | SD_EN=1                                          | 400 | _   | 800  | ps                   | 3       |

| Mismatch in rise/fall time | $\triangle t_{rr} \triangle t_{f}$ | HD/3G/UHD modes                                  | _   | _   | 35   | ps                   | 8       |

|                            | _                                  | SD_EN=0, 5.94Gb/s                                | _   | 18  | _    | ps                   | 4, 5, 8 |

| Duty cycle distortion      | _                                  | SD_EN=0, 2.97Gb/s                                | _   | _   | 14   | ps                   | 4, 5    |

| Duty cycle distortion      | _                                  | SD_EN=0, 1.485Gb/s                               | _   | _   | 20   | ps                   | 4, 5    |

|                            | _                                  | SD_EN=1                                          | _   | _   | 50   | ps                   | 4, 5    |

| Overshoot                  | _                                  | SD_EN=0,                                         | _   | _   | 10   | %                    | 4       |

| Output Return Loss         | ORL                                | 5 MHz – 1.485GHz                                 | 16  | 19  | _    | dB                   | 6       |

|                            |                                    | 1.485GHz – 2.97GHz                               | 12  | 15  | _    | dB                   | 6       |

| Output Voltage Swing       | $V_{OUT}$                          | $R_{SET} = 750\Omega$                            | 750 | 800 | 850  | ${\rm mV_{pp}}$      | 4       |

|                            |                                    | Guaranteed functional.                           | 100 | _   | 2200 | ${\rm mV_{ppd}}$     | _       |

| Input Voltage Swing        | $\triangle V_{DDI}$                | Guaranteed to meet all published specifications. | 250 |     | 2200 | ${\sf mV}_{\sf ppd}$ | _       |

| Output Disable Delay       | _                                  | Any output enabled to all outputs disabled       | _   | _   | 80   | ns                   | _       |

| Output Enable Delay        | _                                  | All outputs disabled to any output enabled.      | _   | _   | 4    | μs                   | _       |

|                            | _                                  | One output enabled to both outputs enabled.      | _   | _   | 500  | ns                   | 7       |

#### Notes:

- 1. The input coupling capacitor must be set accordingly for lower data rates.

- 2. Turning on input trace equalization will reduce jitter in most applications.

- 3. Rise/Fall time measured between 20% and 80% applies to  $800 mV_{pp}$  output swing only.

- 4. Single-ended into a  $75\Omega$  external load.

- 5. Calculated as the actual positive bit-width compared to the expected positive bit-width using a 1010 pattern.

- 6. ORL depends on board design. The GS6081 achieves this specification on Semtech's evaluation boards.

- 7. This Output Enable Delay applies only to the newly enabled output. The output that is already enabled is not impacted in this case.

- 8. Results based on Validation Data using recommended Application Circuit.

# 3. Input/Output Circuits

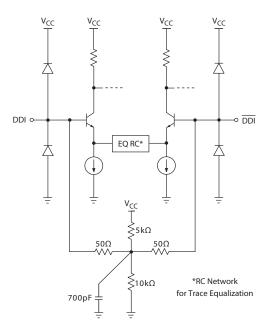

Figure 3-1: Differential Input Stage (DDI/DDI)

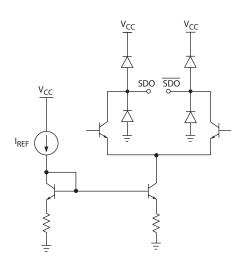

Figure 3-2: Differential Output Stage (SDO1/SDO1, SDO2/SDO2)

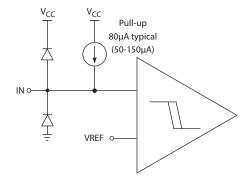

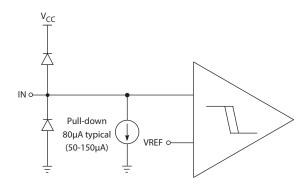

Figure 3-3: Control Input (DISABLE1, SD\_EN, EQ\_EN)

Figure 3-4: Control Input (DISABLE2)

# 4. Detailed Description

### 4.1 Serial Data Input

The GS6081 features a differential input buffer with on-chip  $100\Omega$  differential termination.

The serial data input signal is connected to the DDI and DDI input pins of the device.

Input signals can be single-ended or differential, DC or AC-coupled.

The serial data input buffer is capable of operation with any binary coded signal that meets the input signal level requirements, in the range of 270Mb/s to 5.94Gb/s.

The input circuit is self-biasing to allow for simple AC or DC-coupling of input signals to the device.

### 4.2 Input Trace-equalization

The GS6081 features fixed trace-equalization to compensate for PCB trace dielectric losses.

**Note:** This feature is not available in SD mode, and therefore trace-equalization must be disabled when operating in this mode.

The trace-equalization has two settings, OFF and ON. ON invokes a typical 3dB gain value at 1.5GHz.

**Table 4-1: Input Trace-Equalization**

| EQ_EN    | Function                       |

|----------|--------------------------------|

| 0        | Typical 3dB Trace Equalization |

| 1        | Trace Equalization OFF         |

| Floating | Trace Equalization OFF         |

#### 4.3 Serial Data Output

The GS6081 features dual current-mode differential output drivers capable of driving up to  $1040 \text{mV}_{pp}$  single-ended into a 1m length of  $75\Omega$  cable terminated at both ends.

The output signal amplitude or is set using an external R<sub>SET</sub> resistor.

The SDO1/SDO1 and SDO2/SDO2 pins of the device provide the serial data outputs.

#### 4.3.1 Slew Rate Selection (Rise/Fall Time Requirement)

The GS6081 supports two user-selectable output slew rates.

Control of the slew rate is determined by the setting of the SD\_EN input pin.

**Table 4-2: Slew Rate Selection**

| SD_EN    | Rise/Fall Time                                                 |

|----------|----------------------------------------------------------------|

| 0        | UHD-SDI (5.94Gb/s), SMPTE ST 424 and SMPTE ST<br>292 compliant |

| 1        | SMPTE ST 259 compliant                                         |

| Floating | SMPTE ST 259 compliant                                         |

## 4.4 Output Disable

The GS6081 supports an output disable function for each serial data differential output.

Control of this function is determined by the setting of the serial output disable  $(\overline{DISABLE1})$  and  $\overline{DISABLE2}$  control pins.

Setting this pin LOW, disable power to the current mode serial data output drivers.

**Table 4-3: Output Disable**

| DISABLE1      | DISABLE2      | SDO1/SDO1      | SDO2/SDO2      |

|---------------|---------------|----------------|----------------|

| 0             | 0 or Floating | All Chip Po    | ower Down      |

| 0             | 1             | High-Impedance | Operational    |

| 1 or Floating | 0 or Floating | Operational    | High-Impedance |

| 1 or Floating | 1             | Operational    | Operational    |

When DISABLE1 and DISABLE2 are driven LOW simultaneously, the entire device is powered down, and the power consumption is minimized.

# 4.5 Signal Presence Indicator (SP)

The GS6081 supports a signal presence indicator function.

The signal presence pin  $\overline{(SP)}$  is an active-low output that indicates a signal has been detected at the pre-driver output.

The signal presence function measures signal-edge energy to indicate that the pre-driver to the serial data outputs is toggling.

**Table 4-4: Signal Presence Indicator**

| Pre-Driver Output | SP Pin |

|-------------------|--------|

| Signal present    | 0      |

| No signal present | 1      |

### 4.6 Output Amplitude (RSET)

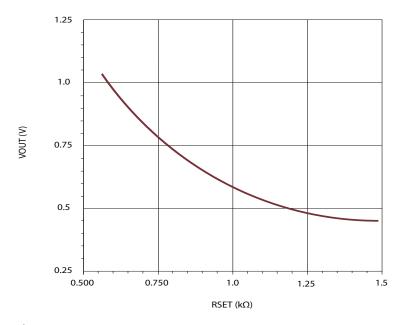

The output amplitude of the GS6081 can be adjusted by changing the value of the  $R_{\text{SET}}$ resistor as shown in Figure 4-1. For an  $800 \text{mV}_{pp}$  output with a nominal  $\pm 7\%$  tolerance, a value of 750 $\Omega$  is required. A ±1% SMT resistor should be used.

The R<sub>SET</sub> resistor is part of an internal DC feedback loop in the GS6081. The resistor should be placed as close as possible to the RSET pin, and connected directly to the  $V_{CC}$ plane (traces/wires may cause instability).

**Note:** Care should be taken when considering layout of the R<sub>SFT</sub> resistor. Please refer to Section 5.1 for more details.

Figure 4-1: V<sub>OUT</sub> vs. R<sub>SET</sub>

In order to determine the best starting value for R<sub>SET</sub>, the following formula should be used:

#### Rset = 8\*(Rtrm/VoutppSE)

PDS-060046

Where **VoutppSE** is in Volts, and both resistances are in  $\Omega$ .

July 2014

Rtrm is the value of the termination resistors, which should be equal to the characteristic impedance of the cable, and is typically 75 $\Omega$ .

The cable must be short ( $\leq 1$ m), and terminated at both ends for the formula to be valid.

Example: For a 75 $\Omega$  cable, Rtrm = 75 $\Omega$  (at both ends), VoutppSE = 800mV<sub>pp</sub>

#### Rset = $8*(75/0.8) = 750\Omega$

This formula is not valid for long, unterminated, or improperly terminated cables.

This formula should be considered as a starting point, and actual swing values may vary based on layout.

**Table 4-5: Typical R<sub>SET</sub> Values**

| Output Swing (mV <sub>pp</sub> ) | $R_{SET}(\Omega)$ |

|----------------------------------|-------------------|

| 1040                             | 576               |

| 800                              | 750               |

| 500                              | 1210              |

### **4.7 Output Return Loss Measurement**

The GS6081 has a feature designed to facilitate reliable output return loss (ORL) measurement while the device is still powered. The device can be put into a BALANCE mode which prevents the outputs from toggling while the device is powered on, allowing the ORL to be measured while the device is still powered.

When  $\overline{EQ\_EN}$  is LOW while SD\_EN is HIGH, the device goes into BALANCE mode. This mode is used during ORL measurement, disabling the AC signal path of the device without powering it down. When in BALANCE mode, the device produces equal pull-down currents in both differential shoulders of both serial data differential outputs, effectively stopping all outputs at the output common mode voltage level. Semtech recommends using BALANCE mode when measuring ORL with +2.5V termination voltage.

# 5. Application Information

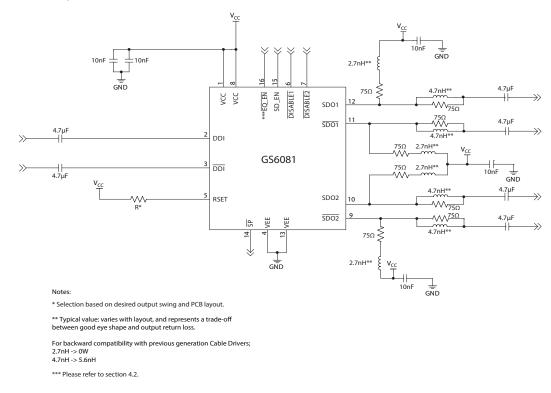

#### 5.1 PCB Layout

Special attention must be paid to component layout when designing serial digital interfaces for HDTV.

An FR-4 dielectric can be used, however, controlled impedance transmission lines are required for PCB traces longer than approximately 1cm. Note the following PCB artwork features used to optimize performance:

- The PCB trace width for HD rate signals is closely matched to SMT component width to minimize reflections due to changes in trace impedance

- The PCB ground plane is removed under the GS6081 output components to minimize parasitic capacitance (**Note:** care should be taken, as removing too much of the plane will make the system susceptible to EMI)

- The PCB ground plane is removed under the GS6081 RSET pin and resistor to minimize parasitic capacitance. The R<sub>SET</sub> resistor should be directly connected to the VCC plane

- Input and output BNC connectors are surface mounted in-line to eliminate a transmission line stub caused by a BNC mounting via high-speed traces

- High-speed traces are round-curved (rather than 45° or 90° angles) to minimize impedance variations due to change of PCB trace width

### **5.2 Typical Application Circuit**

**Figure 5-1: Typical Application Circuit**

# 6. Package & Ordering Information

## **6.1 Package Dimensions**

Figure 6-1: Package Dimensions

# **6.2 Recommended PCB Footprint**

**Figure 6-2: Recommended PCB Footprint**

The Center Pad should be connected to the most negative power supply plane (VEE) by a minimum of 5 vias.

**Note:** Suggested dimensions only. Final dimensions should conform to customer design rules and process optimizations.

## 6.3 Packaging Data

**Table 6-1: Packaging Data**

| Parameter                                                                                | Value                              |

|------------------------------------------------------------------------------------------|------------------------------------|

| Package type / dimensions / pad pitch                                                    | 16-pin QFN / 4mm x 4mm /<br>0.65mm |

| Package Drawing Reference                                                                | JEDEC M0220                        |

| Moisture Sensitivity Level                                                               | 1                                  |

| Junction to Case Thermal Resistance, $\theta_{j-c}$                                      | 31.0°C/W                           |

| Junction to Air Thermal Resistance, $\boldsymbol{\theta}_{j\text{-}a}$ (at zero airflow) | 43.8°C/W                           |

| Psi, Ψ                                                                                   | 11.0°C/W                           |

| Pb-free and RoHS compliant, Halogen-free                                                 | Yes                                |

### **6.4 Solder Reflow Profiles**

The device is manufactured with Matte-Sn terminations and is compatible with both standard eutectic and Pb-free solder reflow profiles. MSL qualification was performed using the maximum Pb-free reflow profile shown in Figure 6-3.

Figure 6-3: Maximum Pb-free Solder Reflow Profile

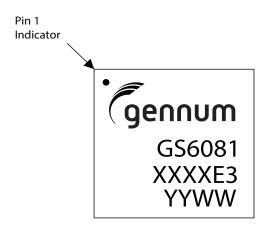

## 6.5 Marking Diagram

July 2014

Figure 6-4: Marking Diagram

PDS-060046

XXXX - Last 4 digits (excluding decimal) of SAP Batch Assembly (FIN) as listed on Packing Slip.

E3 - Pb-free & Green indicator

YYWW - Date Code

# **6.6 Ordering Information**

**Table 6-2: Ordering Information**

|        | Part Number  | Package                  | Temperature Range |

|--------|--------------|--------------------------|-------------------|

| GS6081 | GS6081-INE3  | 16-pin QFN               | -40°C to 85°C     |

| GS6081 | GS6081-INTE3 | 16-pin QFN<br>250pc Reel | -40°C to 85°C     |

### DOCUMENT IDENTIFICATION FINAL DATA SHEET

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice.

#### **CAUTION**

ELECTROSTATIC SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

#### © Semtech 2012

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com